# Comparison of Power Dissipation and Delay of Two Stage and Three stage Voltage Sense Amplifier

## Smriti Shubhanand<sup>1</sup>, Himani Sharma<sup>2</sup>, Deepanshi Agarwal<sup>3</sup>, Parul Gangwar<sup>4</sup>, Akanksha Oli<sup>5</sup>

<sup>1</sup>Assistant Professor, S.R.M.S. Women's College of Engineering and Technology. <sup>2,3,4,5</sup> UG Students, S.R.M.S. Women's College of Engineering and Technology

*Abstract*— A three stage Voltage Sense Amplifier (VSA) with two inputs and single ended output is presented. A Sense Amplifier is responsible for detecting small input level differences at bit line voltages and amplifying it into a signal level that could be easily recognized as either high or low voltages. Cross coupled inverter is used for sensing the two differential inputs obtained from input stage. Results are obtained using CMOS technology in tanner environment. Latch-type voltage Sense Amplifier uses high impedance positive feedback mechanism. Delay and Power Dissipation are experimentally calculated. Total propogation delay of 26.08ns and power dissipation of 13.13 milliwatt is obtained in three stage Sense Amplifier.

*Index Terms*—Voltage Sense Amplifier, Cross Coupled Inverter, CMOS technology, Voltage Sensing, Latch-Type VSA.

#### I. INTRODUCTION

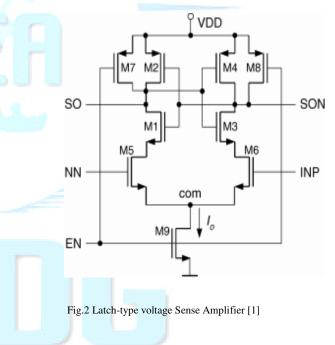

SENSE Amplifiers are the basic circuits that are used in memory devices due to their ability for fast response and decisions. The Latch-Type Voltage Sense Amplifier circuits are used for obtaining the recognized voltage levels for the corresponding voltage levels on bit lines of memory devices. The conventional type voltage Sense Amplifier circuits provide high delays in decision making.

Fig.1. Block Diagram of Two stage Sense Amplifier

The above figure shows the block diagram of conventional Latch-type Voltage Sense Amplifier with double ended output. The first stage is the input differential Amplifier stage which provides the differential input to the sensing stage

. The sensing stage is a cross coupled inverter. The Sense

Amplifiers based on voltage sensing are widely used but this principle application of Sense Amplifiers becomes slow for low supply voltages and large memory designing. Various results are obtained at different values of the input DC level but accurate results are obtained at 0.7V.

#### II. PROPOSED THREE STAGE VOLTAGE SENSE AMPLIFIER

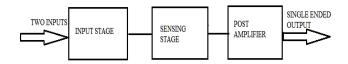

The conventional Voltage Sense Amplifier circuit contains two stages and two outputs are obtained. The three stage Sense Amplifier contains input stage, sensing stage and post Amplifier stage. The post Amplifier stage is used to give single ended output.

Fig.3. Block diagram of Three Stage Sense Amplifier

#### A. INPUT STAGE:

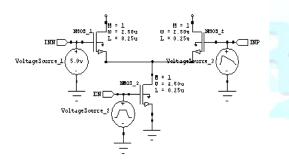

The input stage is a differential Amplifier circuit that provides differential output to sensing stage. The two inputs given to differential stage are INP and INN where INN is a constant DC level of 0.7V and INP piece-wise linear (PWL) voltage. Figure 4 shows the input differential stage of Sense Amplifier where to inputs INN and INP are taken.

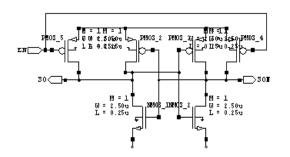

Fig.4. Differential Input Stage

#### B. SENSING STAGE:

Second stage is sensing stage which comprises of cross coupled inverter and two outputs SO and SON are obtained. The outputs are obtained on the transition of the enable signal. Figure 5. shows the sensing stage of Sense Amplifier.

Fig.5. Cross coupled inverter in sensing stage giving two outputs.

#### C. POST AMPLIFIER STAGE:

The sensing stage provide double ended output therefore the third stage is employed so as to convert the output in single ended, this is done using post Amplifier. Fig shows the post

> **WWW.ijreat.org** Published by: PIONEER RESEARCH & DEVELOPMENT GROUP (www.prdg.org)

Amplifier used as third stage in Sense Amplifier.

Fig.6. Post Amplifier as third stage for giving a single ended output

#### **III. TRANSIENT BEHAVIOUR**

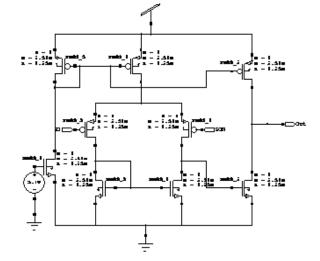

The transient behavior is shown in fig.7. The current is not drawn in off stage and only leakage current is associated with the MOSFETs. The signals INN and INP are inputs to the transistors NMOS 1 and NMOS 2. Transistors NMOS 1 and NMOS\_2 are differential Amplifier that give the differential input to the cross coupled inverter formed by transistors PMOS\_3, PMOS\_2, NMOS\_1 and NMOS\_1. The output terminals SO and SON are pulled to V<sub>DD</sub> by transistors PMOS\_5 and PMOS\_4. The enable signal starts the sensing operation by turning on transistor NMOS\_2. When EN signal is high then circuit is pulled up and when EN is low circuit is pulled down. When EN is high and the inputs are applied on transistors NMOS\_1 and NMOS\_2 we assume that SON is in high state then transistor PMOS\_2 is turned off and we get a low output corresponding to SO. The current flow stops when EN is low.

2

### IJREAT International Journal of Research in Engineering & Advanced Technology, Volume 2, Issue 2, Apr-May, 2014 ISSN: 2320 - 8791

The two outputs of stage two are applied to third stage NMOS\_1 and NMOS\_2 which are driven by the two load transistors PMOS\_5 and PMOS\_1 whose output drives

#### **IV. RESULTS**

PMOS 2 which generates the overall output voltage V(out).

and SO, outputs of second stage

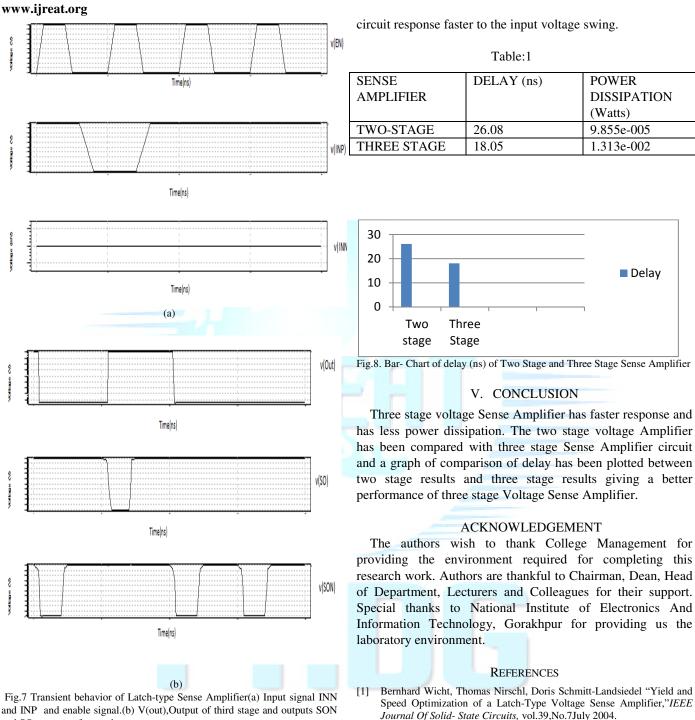

The results of two Stage Sense Amplifier and three Stage Sense Amplifier are compared. The comparison has been done using Tanner Environment. Delay of circuit is improved and

#### [2] Sherwin Paul R. ALmazan, Jestoni V. Zarsuela, Anastacia P. Ballesil, Louis P. Alarcon " A Study on the Effect of Varying Voltage Supply on the Performance of Voltage Sense Amplifiers for 1-Transistor DRAM Memories," *ICSE 2008 Proc. 2008* Johor Bahur, Malaysia.

- [3] Bernard Wicht, Doris Schmitt-Landsiedel, Steffen Paul "A simple Low Voltage Current Sense Amplifier with Switchable Input Transistor.

- [4] Smriti Shubhanand, Dr. H.P.Shukla, A.G.Rao"Design and Simulation of High Speed CMOS Comparator" *International Journal of Electronics* and Communication Engineering, ISSN 0974-2166, Vol.6, Number 1(2013),pp.75-80

- [5] J.R. Cavaliere, W.J. Scarpero," Sense Amplifier," U.S. Patent, N 3879621, April 22, 1975

#### IJREAT International Journal of Research in Engineering & Advanced Technology, Volume 2, Issue 2, Apr-May, 2014 ISSN: 2320 - 8791

#### www.ijreat.org

- [6] G.V. Kritovaski, Y.L. Pogrebnoy," New Sense Amplifier for Small Swing CMOS Logic Circuit," IEEE TCAS-II: Analog and Digital Signal Processing, VOL 47, No.6 June 2000.

- [7] Robert Boylestad, "*Electronic Devices and Circuit Theory*," 9<sup>th</sup> Edition, Pearson Education India. ISBN 9780131189058.

- [8] Adel S. Sedra, Kenneth C. Smith "Microelectronics Circuits" 6<sup>th</sup> Edition, Oxford University Press, ISBN 9780195323030

- [9] M. Matsui, H. Hara, Y. Uetani, L.-S. Kim, T. Nagamatsu, Y. Wanatabe, A. Chiba, K. Matsuda, and T. Sakurai, "A 200 MHz 13 {\u03c4 hbox{mm}}^{2}\$2-D DCT macrocell using sense-amplifying pipeline flip-flop scheme", *IEEE J. Solid-State Circuits*, vol. 29.

- [10] B. Nikoli&cacute,, V. Stojanovi&cacute,, V. G. Oklobd&zcaron,ija, W. Jia, J. Chiu, and M. Leung, "Sense amplifier-based flip-flop", *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp.282 -283, 468 1999

- [11] T. Kobayashi, K. Nogami, T. Shirotori, and Y. Fujimoto, "A currentcontolled latch sense amplifier and a static power-saving input buffer for low-power architecture", *IEEE J. Solid-State Circuits*, vol. 28, pp.523 -527 1993

- [12] J. M. Hill and J. Lachman, "A 900 MHz 2.25 MB cache with on-chip CPU&mdash,now in Cu SOI", *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp.176 -177, 444 2001

- [13] Lin J.T. and Hsu C.C., "An Initial Overdriven Sense Amplifier for Low Voltage DRAMS", IEEE International Conference on Device, Circuits and Systems, 2000.

- [14] Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill, 2001

- [15] B. Nikolic et al., "Improved Sense-Amplifier-Based Flip-Flop: Design and Measurements," IEEE J. Solid-State Circuits, pp. 876-884, June, 2000

- [16] D. Johns and K. Martin, Analog Integrated Circuit Design, 2000 :Wiley

- [17] S. J. Lovett, G. A. Gibbs, and A. Pancholy, "Yield and matching implications for static RAM memory array and sense-amplifier design", *IEEE J. Solid-State Circuits*, vol. 35, pp.1200-1204 2000.

- [18] W. T. Lynch and H. J. Boll, "Optimization of the latching pulse for dynamic flip-flop sensors", *IEEE J. Solid-State Circuits*, vol. SC-9, pp.49 -55 1974

- [19] B. Wicht, Current Sense Amplifiers for Embedded SRAM in High-Performance System-on-a-Chip Designs, 2003 :Springer Verlag